半導(dǎo)體生產(chǎn)流程由晶圓制造,晶圓測(cè)試,芯片封裝和封裝后測(cè)試組成,晶圓制造和芯片封裝討論較多,而測(cè)試環(huán)節(jié)的相關(guān)知識(shí)經(jīng)常被邊緣化,下面集中介紹集成電路芯片測(cè)試的相關(guān)內(nèi)容,主要集中在WAT,CP和FT三個(gè)環(huán)節(jié)。

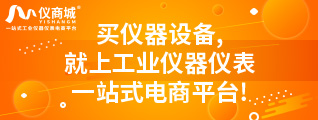

圖1 集成電路設(shè)計(jì)、制造、封裝流程示意圖

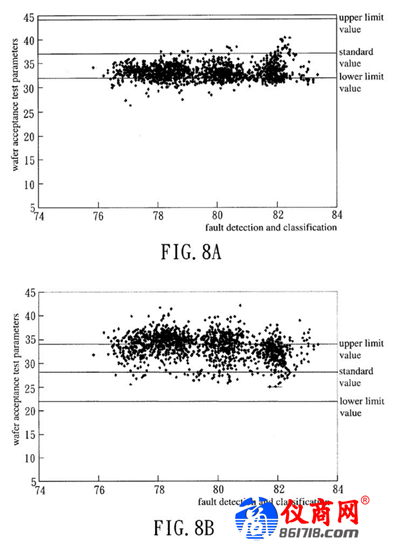

WAT(Wafer Acceptance Test)測(cè)試,也叫PCM(Process Control Monitoring),對(duì)Wafer 劃片槽(Scribe Line)測(cè)試鍵(Test Key)的測(cè)試,通過電性參數(shù)來監(jiān)控各步工藝是否正常和穩(wěn)定,例如CMOS的電容,電阻, Contact,metal Line 等,一般在wafer完成制程前,是Wafer從Fab廠出貨到封測(cè)廠的依據(jù),測(cè)試方法是用Probe Card扎在Test Key的metal Pad上,Probe Card另一端接在WAT測(cè)試機(jī)臺(tái)上,由WAT Recipe自動(dòng)控制測(cè)試位置和內(nèi)容,測(cè)完某條Test Key后,Probe Card會(huì)自動(dòng)移到下一條Test Key,直到整片Wafer測(cè)試完成。 WAT測(cè)試有問題,超過SPEC,一般對(duì)應(yīng)Fab各個(gè)Module制程工藝或者機(jī)臺(tái)Shift,例如Litho OVL異常,ETCH CD 偏小,PVD TK偏大等等。WAT有嚴(yán)重問題的Wafer會(huì)直接報(bào)廢。

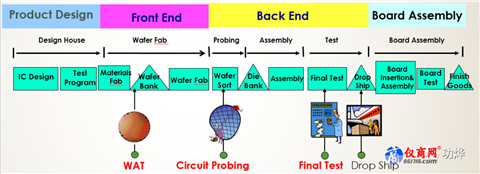

圖2 Test Key示意圖

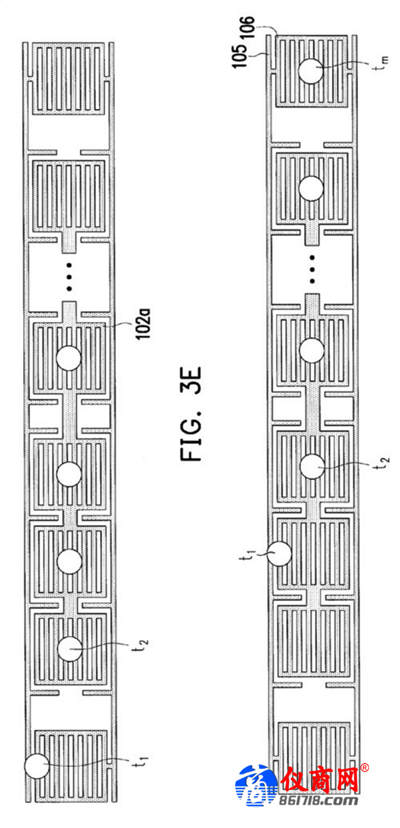

圖3 WAT Probe Card 示意圖

圖4 WAT data chart

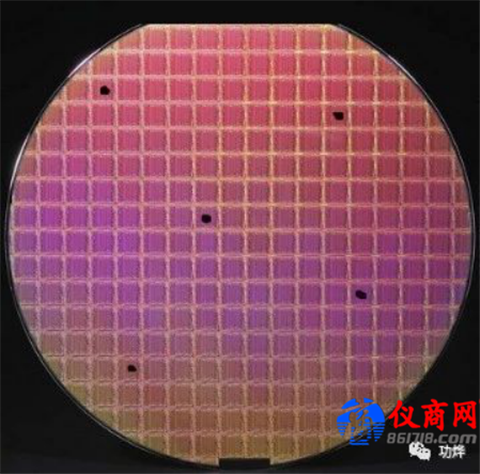

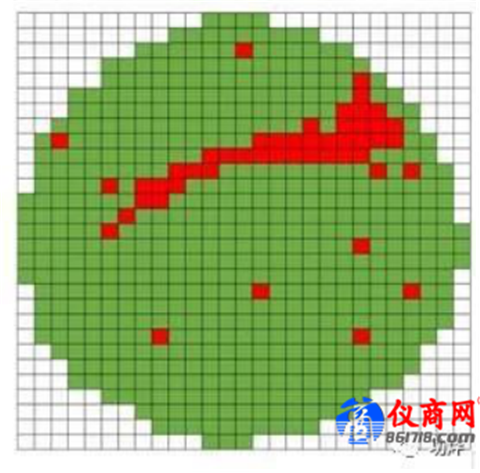

CP(Circuit Probing)也叫“Wafer Probe”或者“Die Sort”,是對(duì)整片Wafer的每個(gè)Die的基本器件參數(shù)進(jìn)行測(cè)試,例如Vt(閾值電壓),Rdson(導(dǎo)通電阻),BVdss(源漏擊穿電壓),Igss(柵源漏電流),Idss(漏源漏電流)等,把壞的Die挑出來,會(huì)用墨點(diǎn)(Ink)標(biāo)記,可以減少封裝和測(cè)試的成本,CP pass才會(huì)封裝,一般測(cè)試機(jī)臺(tái)的電壓和功率不高,CP是對(duì)Wafer的Die進(jìn)行測(cè)試,檢查Fab廠制造的工藝水平。

圖5 黑點(diǎn)為ink

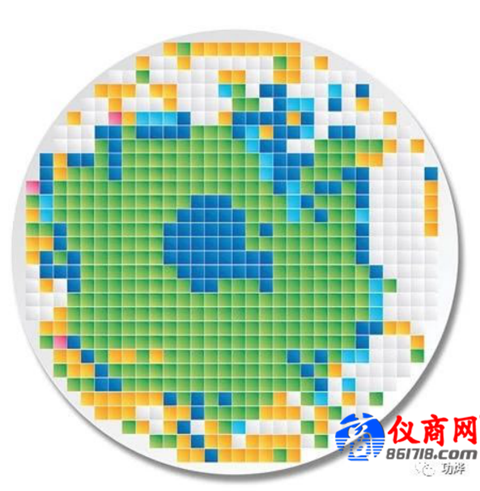

圖6 CP Bin Map示意圖

CP測(cè)試程序和測(cè)試方法優(yōu)化是Test Engineer努力的方向,下面介紹幾種降低CP測(cè)試成本的方法。

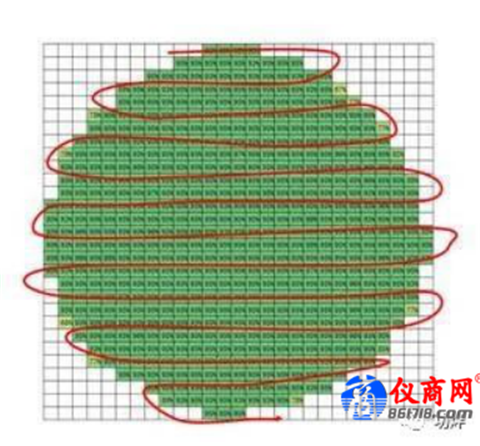

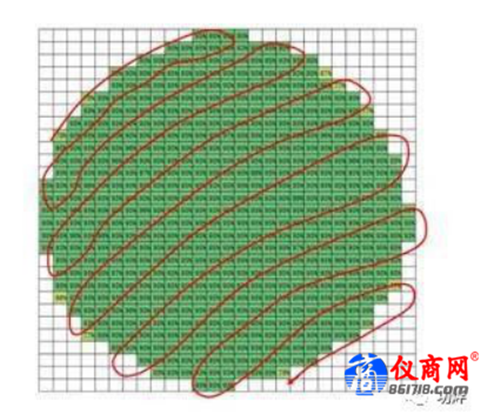

1.同一個(gè)Probe Card可以同時(shí)測(cè)多個(gè)Die,如何排列可以減少測(cè)試時(shí)間?假設(shè)Probe Card可以同時(shí)測(cè)6個(gè)Die,那么是2×3排列還是3×2,或者1×6,都會(huì)對(duì)扎針次數(shù)產(chǎn)生影響,不同的走針方向,也會(huì)產(chǎn)生Test時(shí)間問題。

圖7 不同走向示意圖

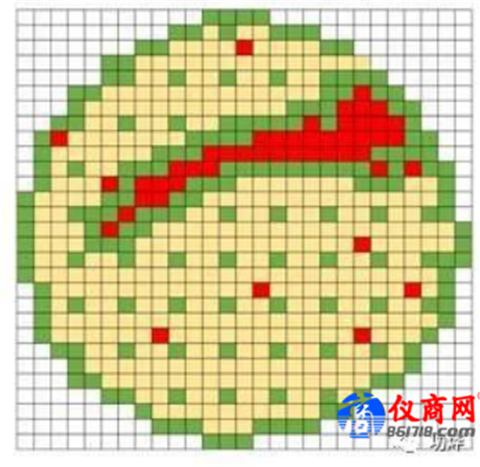

2.隨著晶圓尺寸越來越大,晶圓上的Die越來越多,很多公司CP Test會(huì)采用抽樣檢查(Sampling Test)的方式來減少測(cè)試時(shí)間,至于如何抽樣,涉及不同的Test Recipe,一些大數(shù)據(jù)實(shí)時(shí)監(jiān)控軟件可以在測(cè)試的同時(shí)按照一定算法控制走針方向,例如抽測(cè)到一個(gè)Die失效后,Probe Card會(huì)自動(dòng)圍繞這個(gè)Die周圍一圈測(cè)試,直到測(cè)試沒有問題,再進(jìn)行下一個(gè)Die的抽測(cè),這種方法可以明顯縮短測(cè)試時(shí)間。

圖8 full map 與 sample test示意圖

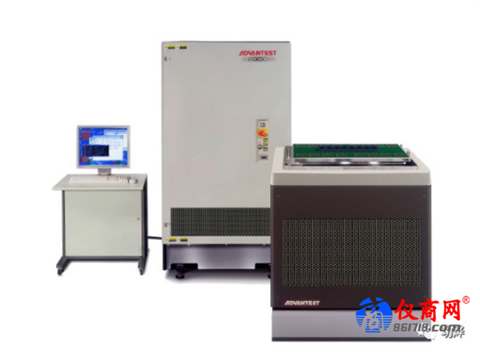

FT(final test)是對(duì)封裝好的Chip進(jìn)行Device應(yīng)用方面的測(cè)試,把壞的chip挑出來,F(xiàn)T pass后還會(huì)進(jìn)行process qual和product qual,F(xiàn)T是對(duì)package進(jìn)行測(cè)試,檢查封裝造廠的工藝水平。FT的良率一般都不錯(cuò),但由于FT測(cè)試比CP包含更多的項(xiàng)目,也會(huì)遇到Low Yield問題,而且這種情況比較復(fù)雜,一般很難找到root cause。廣義上的FT也稱為ATE(Automatic Test Equipment),一般情況下,ATE通過后可以出貨給客戶,但對(duì)于要求比較高的公司或產(chǎn)品,F(xiàn)T測(cè)試通過之后,還有SLT(System Level Test)測(cè)試,也稱為Bench Test。SLT測(cè)試比ATE測(cè)試更嚴(yán)格,一般是Function的Test,測(cè)試具體模塊的功能是否正常,當(dāng)然SLT更耗時(shí)間,一般采取抽樣的方式測(cè)試。

圖9 FT tester 示意圖

小結(jié)一下,WAT是在晶圓制造過程中進(jìn)行的測(cè)試,通過對(duì)Die與Die之間Scribe Line的Test Key電學(xué)性能的測(cè)試,來監(jiān)控Fab制程的穩(wěn)定性;CP測(cè)試是制造完成后,封測(cè)之前進(jìn)行的電學(xué)測(cè)試,把壞的Die標(biāo)記出來,減少封裝的成本;FT是Die切割,打磨,封裝后進(jìn)行器件功能性的測(cè)試,可以評(píng)價(jià)封測(cè)廠的封裝水平,只有所有的測(cè)試都通過后,才可以應(yīng)用到產(chǎn)品上。